2.2 中断系统

中断是计算机技术中的一个重要概念。中断的存在使计算机的工作效率大大提高,几乎所有微控制器(MCU,或称单片机)和微处理器(CPU)都配置有中断功能。下面首先阐述其概念。

2.2.1 中断的基本概念

中断是计算机中的一个十分重要的概念,那么什么是中断呢?不妨先看一下下面这个例子:假如你正在自习室看书,坐在你前面的小张问你一道题;于是你把书折个角,转身为小张讲题;当你正在给他讲题时,你的手机响了,于是你让小张稍等一下,出去接电话;你接电话后,回来继续给小张讲题;讲完题,你打开书,从刚才被打断的地方继续看下去。这就是我们日常生活中的“中断”现象。从看书到给小张讲题是一次中断过程,而从给小张讲题到出去接电话则是在中断过程中发生的又一次中断,也就是所谓的“中断的嵌套”。计算机技术中的中断概念与此相似。

在计算机系统中,当CPU正在执行当前程序的过程中,由于某种突发事件的发生,如有键按下,使它暂停当前的操作,转去执行另一段程序,待这段程序执行完毕后,再返回到原来被打断的地方继续执行,这就是一次典型的中断过程。中断控制方式使CPU在平时可以利用充分的时间去处理主要事件,而当外界有特殊情况需要处理时CPU也不会错过,这样的工作效率较高。在编制实时性要求较高的程序中,中断控制方式显得特别有用。实际上,在一般的单片机多任务(如数据采集、计算、通信等)的应用程序编制中,中断编程是必不可少的一部分。

下面介绍几个关于中断的基本概念。

(1)中断源:引起中断发生的事件被称为中断源。

(2)中断请求:中断源向CPU发出的请求中断处理信号。

(3)中断响应:CPU收到中断请求后转相应的事件处理程序。

(4)现场保护:在处理新任务时可能破坏原有的工作现场,所以需要对工作现场和工作环境进行适当的保护,以使执行完新任务后可以回到原来的工作现场继续工作。

(5)中断返回:将被打断的工作断点找回来,继续执行原先被打断的工作。

(6)关中断:不允许CPU响应中断。

(7)开中断:允许CPU响应中断。

(8)中断屏蔽:通过设置有关的中断屏蔽位禁止响应某个中断。

(9)中断矢量:即中断服务程序的入口地址。每个中断源都有自己固定的“中断矢量”,不可任意挪用或更改。CPU接到中断请求时,转向对应的中断服务程序的入口地址来执行中断服务程序。一个中断矢量可以只对应一个中断源,也可以对应多个中断源。当多个中断源对应一个中断矢量时,就需要在中断服务程序中判断是哪个中断源发出的中断申请,进而执行响应的中断服务程序。

(10)中断优先级:当几个中断源同时向CPU发出中断申请时,优先级别较高的中断率先得到响应。

2.2.2 PIC16F87X的中断源及中断逻辑

1.PIC16F87X的中断源

PIC16F87X系列单片机有多达14个中断源,具体数目根据单片机型号的不同而有所差异,如表2-9所示。中断控制寄存器INTCON标志着各个中断源的请求。PIC16F87X系列单片机虽然有着丰富的中断源,但只有一个中断矢量(0004h),并且各个中断源之间没有优先级的差别,也没有非屏蔽中断(如80C196KC中的NMI中断),所以这也是PIC16F87X系列单片机的一个缺陷。由于PIC单片机所有中断源均指向0004H这个中断矢量,所以在进入中断服务程序时,并不知道是哪个中断源产生的,所以必须通过检测所有开放中断的标志位来判断究竟是哪个中断源发出的中断。此外,从检查中断标志位的顺序,可以人为地设定中断源的优先级,先检查优先级较高的。在多个中断源同时发出中断申请时,即可按优先级来逐项处理,或是清除其他优先级别较低的中断标志位。

表2-9 PIC16F87X系列单片机中断源一览表

下面对表2-9中所列各中断源的特点作简要介绍。

(1)外部中断(INT Pin Interrupt)

外部中断的引脚为RB0/INT,这是一个边沿触发的中断:当INTEDG(OPTION<6>)==1时,由上升沿触发;当OPTION<6>)=0时,由下降沿触发。当RB0/INT引脚上检测到有效的跳变沿时,系统硬件会自动将外部中断标志位INTF置1。该中断可由INTE位屏蔽(INT=0)或使能(INT=1)。注意,执行完外部中断服务程序后,INTF不会由硬件自动清零,需由用户编程清零。如果INTE在单片机进入睡眠状态前已经被置位,则外部中断INT可以将芯片从睡眠状态中唤醒。唤醒以后程序的去向取决于全局中断位GIE。

(2)TMR0溢出中断(TMR0 Overflow Interrupt)

当定时/计数器Timer0的TMR0寄存器溢出(由0FFh→00h)时,TMR0中断标志位T0IF(INTCON<2>)被硬件置1,产生中断。该中断屏蔽/使能位为T0IE(INTCON<5>),通过对该位的清零或置位可以禁止或允许TMRO中断。

(3)RB口电平变化中断(PORTB Change Interrupt)

PORTB<7∶4>引脚具有电平变化中断功能,其中的任何一个引脚上的电平发生变化都会使中断标志位RBIF(INTCON <0>)置1,并向CPU申请中断。为了使读者对该中断有个深入的了解,在此给出了PORTB<7∶4>的引脚原理图,如图2-7所示。

图2-7 PORTB<7∶4>的引脚原理图

由图2-7可以看出,锁存器A每个时钟周期Q1均刷新一次,其输出电平随外部引脚电平变化而变化;锁存器B则只有在对该I/O引脚进行读操作时才刷新一次;两个锁存器的输出作为或非门C的输入,一旦锁存器A和B的输出不一致(说明该引脚有电平变化),或非门输出高电平“1”;或非门C的输出和引脚方向控制寄存器TRIS Latch的输出作为与门D的输入,所以只有当该引脚被配置为输入引脚(TRIS寄存器中对应的位为1),或非门的输出信号才能通过与门;或非门E的4个输入端分别接到PORTB<7∶4>上,从而使RB7:RB4中的任何一个引脚上发生了电平变化,都能引起中断。

注意:1)只有当PORTB<7∶4>被设置为输入引脚时,才具有电平变化中断功能,而被设置为输出的引脚没有中断功能。

2)中断服务程序中对中断标志位RBIF的清零必须遵循下面的步骤:

① 对PORTB进行一次读操作。该指令目的是为了结束失配条件(mismatch condition)。

② 对RBIF位清零。

(4)TMR1溢出中断(TMR1 Overflow Interrupt)

当定时/计数器Timer1的TMR1寄存器对溢出(由0FFFFh→0000h)时,TMR1中断标志位TMR1IF(PIR1<0>)被硬件置1,产生中断。该中断屏蔽/使能位为TMR1IE(PIE1<0>),通过对该位的清零或置位可以禁止或允许CPU响应TMR1溢出中断。

(5)TMR2溢出中断(TMR2 Overflow Interrupt)

定时/计数器Timer2的TMR2寄存器按递增规律计数,从某一起始值(默认状态为00H)开始递增,当与周期寄存器PR2内容相同为止,再增加一次则返回到00H,同时产生高位溢出信号,该溢出信号作为后分频器的计数脉冲。当后分频器产生溢出时,才会将溢出中断标志位TMR2IF(PIR1<1>)置1,向CPU提出中断申请。该中断屏蔽/使能位为TMR2IE(PIE1<2>),通过对该位的清零或置位可以禁止或允许CPU响应TMR溢出中断。

(6)CCP1中断(CCP1 Interrupt)

CCP1模块在两种工作模式下可产生中断:捕捉模式和比较模式。

当CCP1工作在捕捉模式下时,引脚RC2/CCP1上有下列事件发生:出现脉冲上升沿;出现脉冲下降沿;每出现4个脉冲的上升沿,TMR1(TMR1H:TMR1L)的计数值立即被送到CCRP1寄存器(CCPR1H:CCPR1L),CCP1的中断标志位CCP1IF将被硬件自动置1,向CPU申请中断。究竟是哪种事件触发中断,则由CCP1CON寄存器中的CCP1M3~CCP1M0来决定。

当CCP1工作在比较模式下时,系统将对CCP1寄存器与TMR1寄存器的值进行比较。一旦二者相等,就在RC2/CCP1引脚上输出下列3种状态之一:高电平、低电平或保持原来引脚上的电平不变。同时,中断标志位CCP1IF被硬件自动置1,产生一个比较中断。究竟输出哪种状态,则由CCP1CON寄存器的CCP1M3~CCP1M0来决定。

注意:在CPU响应CCP1中断后,必须由软件将中断标志位CCP1IF清零。

(7)CCP2中断(CCP2 Interrupt)

CCP2中断与CCP1中断类似,只是对应的引脚和寄存器不同,其引脚为RC1/T1OSO/CCP2,寄存器为CCPR2和CCP2CON。

(8)SCI发送中断(SCI Transmit Interrupt)

在PIC单片机中,SCI(Serial Communications Interface)也就是所谓的USART。USART可以工作在同步或异步模式。USART发送器由发送移位寄存器TSR和发送缓冲寄存器TXREG构成。不论USART工作在哪种模式下,一旦TXREG中的数据送入TSR,中断标志位TXIF就会被硬件自动置1,并向CPU申请中断。TXIF置位后不能被软件清零,只有在下一个要发送的数据送入TXREG后,TXIF才能复位。

(9)SCI接收中断(SCI Receive Interrupt)

USART接收器主要由接收移位寄存器RSR和接收缓冲寄存器组成。不论USART工作在哪种模式下,一旦RSR将数据装载到RCREG中,中断标志位RCIF就会被硬件自动置1,向CPU申请中断。当RCREG被读出时,RCIF被清零。

(10)SSP中断(SSP Interrupt)

不论SSP模块工作在SPI模式、I2C从动模式还是I2C主控模式,一个发送或接收动作都会将SSP中断标志位SSPIF置1,从而引起中断。此外,当SSP工作在I2C主控模式下时,下列事件也会引起SSP中断:启动信号完成、停止信号完成、重启信号完成、应答信号完成、当SSP模块空闲时出现了启动信号或停止信号(在多主系统中)。SSPIF被置位后,必须在中断返回时,用软件将SSPIF清零。

(11)SSP、I2C总线冲突中断(I2C Bus Collision Interrupt)

当SSP模块被配置为I2C模式时,总线冲突会将中断标志位BCLIF置1,引起I2C总线冲突中断。

(12)并行从口中断(Parallel Slave Port Interrupt)

当并行从口发生读操作或写操作时,中断标志位PSPIF将会被置1,引起并行从口中断。中断标志位必须被软件清零。

(13)A/D转换结束中断(A/D Conversion Complete Interrupt)

当一次A/D转换结束后,中断标志位ADIF将会被硬件自动置1,引起中断。当把结果寄存器ADRES的值读走后,ADIF自动清零。

(14)E2PROM写操作完成中断(Data E2PROM Write Complete Interrupt)

对E2PROM进行写操作时,一旦写操作完成,标志位EEIF被置1,向CPU发出中断申请。注意,EEIF必须在置位WR控制位(EECON1<1>)之前用软件清零。

2.PIC16F87X的中断逻辑

在PIC16F87X系列中,不同型号的单片机所对应的中断逻辑电路也略有不同,主要体现在中断源的种类和数量的不同,从如图2-8所示的PIC16F87X中断逻辑图中可看出每一种中断源都对应着两个控制位:中断标志位XXXF(xxx Flag)和中断使能位XXXE(xxx Enable,或称中断屏蔽位)。当某一种中断源满足一定的触发条件时,对应的中断标志位就会由硬件自动置1,并向CPU提出中断申请。需要注意的是,中断标志位的清零及中断屏蔽位的置1或清零也是由用户通过程序来完成的。

图2-8 PIC16F87X中断逻辑图

注意:(1)PIC16F870不具备PSPIF、SSPIF、CCP2IF和BCLIF中断源。

(2)PIC16F871不具备SSPIF、CCP2IF和BCLIF中断源。

(3)PIC16F872不具备PSPIF、RCIF、TXIF和CCP2IF中断源。

(4)PIC16F873/876不具备PSPIF中断源。

(5)PIC16F877具备图2-8中所有中断源。

如图2-8所示,可以把14种中断源分为两个级别。第一级别包括3个中断源:T0IF、INTF和RBIF。该级别的中断源向CPU提出中断申请后,要“连闯两关”才能得到CPU的响应。以INTF为例,当RB0/INT引脚上出现跳变沿(上升沿/下降沿)时,INTF就会被硬件自动置1,向CPU提出中断申请;“第一关”是外部中断使能/屏蔽位INTE,如果INTE为1,表明允许INTF中断,否则INTF在第一关被“毙”;接下来闯“第二关”——全局中断使能/屏蔽位GIE(Global Interrupt Enable),如果GIE=1,则INF中断申请被放行,可以得到CPU的响应,否则INTF在第二关被“毙”。第二级别包括剩下的11个中断源,也就是外围中断。这个级别的中断源要想得到CPU的响应,需“连闯三关”。以ADIF为例,这三关依次是:ADIE→PEIE→GIE,其中PEIE是外设中断屏蔽位。

2.2.3 与中断相关的寄存器

与中断相关的寄存器共有5个,分别是选项寄存器OPTION_REG、中断控制寄存器INTCON、第一外设中断标志寄存器PIR1,第一外设中断屏蔽寄存器PIE1,第二外设中断标志寄存器PIR2和第二外设中断屏蔽寄存器PIE2。下面只对各寄存器中与中断有关的位进行介绍:

1.选项寄存器OPTION_REG(地址为81H/181H)

● bit 6 INTEDG:外部中断边沿选择位。

➢ 1:RB0/INT引脚上升沿触发中断。

➢ 0:RB0/INT引脚下降沿触发中断。

2.中断控制寄存器INTCON(地址为0BH/SBH/10BH/18BH)

● bit 7 GIE:全局中断屏蔽位。

➢ 1:允许所有的未被屏蔽的中断。

➢ 0:禁止一切中断。

● bit 6 PEIE:外围中断屏蔽位。

➢ 1:允许所有的未被屏蔽的外围中断。

➢ 0:禁止所有的外围中断。

● bit 5 T0IE:TMR0溢出中断屏蔽位。

➢ 1:允许TMR0溢出中断。

➢ 0:禁止TMR0溢出中断。

● bit 4 INTE:外部中断屏蔽位。

➢ 1:12B0/INT引脚上升沿触发中断。

➢ 0:12B0/INT引脚下降沿触发中断。

● bit 3 RBIE:RB7~RB4电平变化中断屏蔽位。

➢ 1:允许PORTB口电平变化中断。

➢ 0:禁止PORTB口电平变化中断。

● bit 2 T0IF:TMR0溢出中断标志位。

➢ 1:TMR寄存器已经溢出(必须由软件清零)。

➢ 0:TMR寄存器没有溢出。

● bitl INTF:外部中断标志位。

➢ 1:INT引脚出现中断触发信号(必须由软件清零)。

➢ 0:INT引脚无中断触发信号。

● bit0 RBIF:RB7~RB4电平变化中断标志位。

➢ 1:RB7~RB4已发生了电平变化(必须由软件清零)。

➢ 0:RB7~RB4未发生电平变化。

3.第一外设中断屏蔽寄存器PIE1(地址为8CH)

● bit 7 PSPIE:并行从口中断屏蔽位。只有40脚封装型号具备,对于28脚封装型号总保持零。

➢ 1:允许并行从口读l写中断。

➢ 0:禁止并行从口读l写中断。

● bit ADIE:A/D转换中断屏蔽位。

➢ 1:允许A/D转换中断。

➢ 0:禁止A/D转换中断。

● bit 5 RCIE:串行通信接收中断屏蔽位。

➢ 1:允许USARTA接收中断。

➢ 0:禁止USARTA接收中断。

● bit4 TXIE:串行通信发送中断屏蔽位。

➢ 1:允许USARTA发送中断。

➢ 0:禁止USARTA发送中断。

● bit 3 SSPIE:同步串行端口中断屏蔽位。

➢ 1:允许SSP中断。

➢ 0:禁止SSP中断。

● bit 2 CCP1IE:CCP1模块中断屏蔽位。

➢ 1:允许CCP1中断。

➢ 0:禁止CCP1中断。

● bit1 TMR2IE:TMR2溢出中断屏蔽位。

➢ 1:允许TMR2溢出中断。

➢ 0:禁止TMR2溢出中断。

● bit 0 TMR1IE:TMR1溢出中断屏蔽位。

➢ 1:允许TMR1溢出中断。

➢ 0:禁止TMR1溢出中断。

4.第一外设中断标志寄存器PIR1(地址为0CH)

● bit 7 PSPIF:并行从口中断标志位。只有40脚封装型号具备,对于28脚封装型号总保持零。

➢ 1:并行从口发生了读/写中断请求(必须由软件清零)。

➢ 0:并行从口未发生读/写中断请求

● bit 6 ADIF:A/D转换中断标志位。

➢ 1:A/D转换结束。

➢ 0:A/D转换未结束。

● bit 5 RCIF:串行通信接收中断标志位。

➢ 1:USARTA接收缓冲区满。

➢ 0:USARTA接收缓冲区空。

● bit 4 TXIF:串行通信发送中断标志位。

➢ 1:USARTA发送缓冲区空。

➢ 0:USARTA发送缓冲区满。

● bit 3 SSPIF:同步串行端口中断标志位。

➢ 1:发送/接收完毕。

➢ 0:等待/发送。

● bit 2 CCP1IF:CCP1模块中断标志位。

在捕捉模式下:

➢ 1:发生了TMR1寄存器捕捉中断请求(必须由软件清零)。

➢ 0:未发生TMR1寄存器捕捉中断。

在比较模式下:

➢ 1:发生了TMR1寄存器比较输出中断请求(必须由软件清零)。

➢ 0:未发生TMR1寄存器比较输出中断请求。

● bit 1 TMR2IF:TMR2溢出中断标志位。

➢ 1:发生了TMR2溢出中断(必须由软件清零)。

➢ 0:未发生TMR2溢出中断。

● bit 0 TMR1IF:TMR1溢出中断标志位。

➢ 1:发生了TMR1溢出中断(必须由软件清零)。

➢ 0:未发生TMR1溢出中断。

5.第二外设中断屏蔽寄存器PIE2(地址为8DH)

● bit 6保留位,为0。

● bit 4 EEIE:E2PROM写中断屏蔽位。

➢ 1:允许E2PROM写中断。

➢ 0:禁止E2PROM写中断。

● bit 3 BCLIE:总线碰撞中断屏蔽位(Bus Collision Interrupt Enable bit)。

➢ 1:允许总线碰撞中断。

➢ 0:禁止总线碰撞中断。

● bit 0 CCP2IE:CCP2中断屏蔽位。

➢ 1:允许CCP2中断。

➢ 0:禁止CCP2中断。

6.第二外设中断标志寄存器PIR2(地址为0DH)

● bit 6保留位,为0。

● bit4 EEIF:E2PROM写操作中断标志位。

➢ 1:写操作完成(必须由软件清零)。

➢ 0:写操作未完成或未进行写操作。

● bit 3 BCLIF:总线碰撞中断标志位(Bus Collision Interrupt Flag bit)。

➢ 1:当SSP被配置为I2C主模式时发生了总线碰撞。

➢ 0:未发生总线碰撞中断。

● bit 0 CCP2IF:CCP2中断标志位。

在捕捉模式下:

➢ 1:发生了TMR1寄存器捕捉中断请求(必须由软件清零)。

➢ 0:未发生TMR1寄存器捕捉中断。

在比较模式下:

➢ 1:发生了TMR1寄存器比较输出中断请求(必须由软件清零)。

➢ 0:未发生TMR1寄存器比较输出中断。

2.2.4 CPU对中断的处理

不论各种中断屏蔽位和全局中断屏蔽位为何值,只要某一中断源的中断条件得到满足,单片机就会向CPU发出中断申请,并将响应的中断标志位置1。而该中断是否能得到CPU的响应,则取决于和它相关的中断屏蔽位的值。如果该中断被一路放行,则中断申请被递交给CPU。当CPU响应中断后,全局中断屏蔽位GIE将自动由硬件清零,以免发生重复响应;然后由硬件自动把当前PC指针值压入堆栈,并把PC指针指向中断矢量地址0004H,从而进入中断服务程序开始执行,步骤为:首先CPU对有关寄存器进行保护,再检查各个中断源标志位以确定中断源发出申请的位置,然后把对应的中断标志位清零并转入对应的程序执行。中断服务程序执行完毕后,再执行中断返回指令“RETFIE”退出中断,此时,硬件自动将保存在栈顶的断点地址弹回到PC指针中,使CPU返回继续执行被中断的主程序。

1.中断响应的延迟

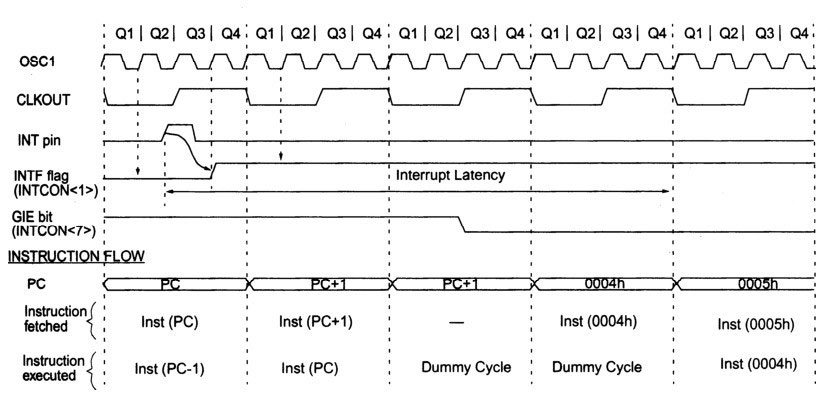

从中断事件发生(即中断标志位被置1)到位于地址0004H的中断服务程序开始执行(即得到CPU的响应)需要一定的时间,该时间被定义为中断响应的延迟时间,有时被形象地称为中断潜伏期(Latency)。同步中断(如内部中断)的延迟时间是3个指令周期。异步中断(如外部中断、INT中断和PORTB口电平变化中断等)的延迟时间为3~3.75个指令周期,在如图2-9所示的INT引脚及其他外部中断时序图中,OSC1是系统时钟脉冲信号,每4个时钟周期对应一个指令周期。只有在RC时钟模式下,CLKOUT引脚才会向外输送指令周期。INT中断是边沿触发的,但对其脉冲宽度的最小值有要求,关于具体内容可参考PIC16F87X的芯片数据资料。当INT中断被触发时,中断标志位INTF自动被硬件置1。系统在每个指令周期的第二个时钟周期的上升沿,对INTF的状态进行一次检查。若检测到INTF信号被置1,则CPU在下一个指令周期内将全局中断屏蔽位GIE清零,禁止一切中断的打扰。接下来的一个指令周期内,中断矢量0004H被载入PC指针。紧接着一个指令周期内,CPU开始执行中断服务程序的第一条指令。可见,从INT引脚发生有效电平跳变到中断服务程序的第一条指令的执行,大约需要经过3~4个指令周期的潜伏期。注意,单周期和双周期指令的中断潜伏期相同。另外,由外部信号,如定时l计数器、捕捉、端口电平变化等触发的中断都有类似的时序。

图2-9 INT引脚及其他外部中断时序图

2.中断现场的保护

现场保护是中断技术中的一个十分重要的概念,其目的是使CPU执行完中断服务程序后,再回到原来的“现场”继续执行。PIC16F87X系列单片机在中断期间,只有返回地址的PC值被压入堆栈,而其他关键的寄存器(如W寄存器、STATUS寄存器等)的值则需要用户自己编程来保护。注意,中断现场的数据不是保存到堆栈中,而是保存到用户选择的一些文件寄存器中,即RAM数据存储器中。Microchip公司为用户提供了一些实现中断现场保护功能的通用程序段,下面只给出适用于PIC16F87X系列单片机的一个程序段,对于其他程序段,用户可参考相关的数据资料。

;**********************************************************************

;中断现场保护程序(适用于PIC16F87X系列单片机)

;此程序段功能:对W寄存器、STATUS和PCLATH进行保护

;说明:W_TEMP、STATUS_TEMP、PCLATH_TEMP为临时寄存器

;**********************************************************************

MOVWF W_TEMP; 复制W寄存器内容到W_TEMP

SWAPF STATUS,W;将STATUS高低字节交换后存入W寄存器

CLRF STATUS; 选择BANKO

HOVWF STATUS_TEMP;保存STATUS内容到STATUS_TEMP

MOVF PCLATH,W;和下一条指令联合将PCLATH内容复制到

MOVWF PCLATH_TEMP;PCLAT_STATUS

CLRF PCLATH; 将PCLATH指向BANK0

;中断服务程序

…

MOVF PCLAT_TEMP,W

MOVWF PCLATH;恢复PCLATH

SWAPF STATU_TEMP,W

MOVWF STATUS;恢复STATUS

SWAPF W_TEMP,F;将W_TEMP内容高低半字节交换

SWAPF W_TEMP,W;将W_TEMP内容高低半字节交换

:后放入W寄存器

中断现场保护的步骤总结如下:

① 保存W寄存器。

② 保存STATUS到BANK0。

③ 保存其他重要的寄存器(若有需要)。

④ 执行中断服务程序。

⑤ 恢复其他重要的寄存器(若有需要)。

⑥ 恢复STATUS寄存器和原来的BANK。

⑦ 恢复W寄存器。

3.中断编程的几点注意事项

(1)在中断服务程序中,一旦确定出发出申请的中断源,就应把中断源标志位手工清零;否则,执行中断返回命令“RETFIE”重开中断后,由于中断标志位仍为1,引起CPU重复响应同一个中断请求。

(2)中断服务程序开始应该进行现场保护,结束前应该恢复现场。寄存器STATUS、W和PCLATH通常一定要加以保护,其他寄存器的保护由用户根据需要来保护。

(3)CPU响应一个中断后,全局中断屏蔽位GIE被自动清零,不再受理其他一切中断申请、中断返回时,GIE自动置1。

(4)如果在处理一次中断的过程中,还有其他更重要的中断需要响应,就要用到中断的嵌套技术,用户需在中断程序中将GIE重新置1,允许响应后续中断。但需注意的是,PIC16F87X的硬件堆栈的深度为8级,因此最多只能嵌套8级中断,否则会造成堆栈溢出。

(5)PIC16F87X系列单片机的一个缺陷就是14种中断源共用一个中断矢量,不存在中断优先级,对一切中断均一视同仁。用户只能通过在中断服务程序中对中断源检查的顺序来实现优先级的功能。

(6)在复位状态下,全局中断使能位和其他所有中断屏蔽位都被清零,禁止CPU响应一切中断。

(7)不论中断屏蔽位的状态如何,只要中断源满足中断条件,中断标志位都会置位。

(8)即使没有用到中断,地址0004H也最好写上一句RETFIE,以使干扰引起误中断信号时能迅速返回。

(9)中断服务程序的最后一条指令必须是中断返回指令RET。

(l0)在进行查表操作期间必须禁止CPU响应中断,以避免中断返回时跳转到不希望的地址上。

(11)当打算通过中断唤醒CPU时,相应的中断使能位必须提前被置为1。在这种情况下,需要在SLEEP指令后设置一条NOP空操作指令。

(12)当CPU正在执行一条对INTCON的“读—修改—写”指令时,如果发生了中断请求,则中断程序会被执行两次,至于原因读者可自行分析。解决办法为:如果在程序中需要对INTCON的某一中断屏蔽位进行修改,则应事先将GIE清零,禁止响应一切中断,修改完成后再将GIE恢复为1。